串行FIR低通滤波器的FPGA设计(论文10000字)

摘 要

生活中处处涉及信号,但它在产生和传播时会掺杂着众多其它无用噪声,严重破坏其质量。由此,滤波技术就显得尤为关键了。为此,人们设计使用滤波器将众多信号中有用部分留下来,将无用信号滤出去。现代工程中优先考虑使用数字系统,它具有高功率、小体积、速度快、性价比高等特征。因此,数字滤波器渐渐成为工程中的宠儿。

有限脉冲响应FIR(Finite Impulse Response)滤波器,顾名思义,抽样数量有限,卷积个数随之确定,具有精准的线性相位特性,传输过程中不产生失真,在生产生活各项工程中广受欢迎。串行滤波器结构简单,实现方便,在对滤波器阶数要求低的系统中普遍应用。

现场可编程门阵列FPGA(Field Programmable Gate Array)属于ASIC中半定制电路。它使用起来很是灵活,通用性强、规模大、体积小、现场可编程,可以完成各种庞杂的数字电路各项功能。这些优点增广了FPGA在生产生活中的普及范围,受到大众的喜爱。

Verilog HDL语言在设计数字电路方面十分普及。它简洁高效、方便使用,同时功能还很强大,对各种工程设计人员都很适用。利用Verilog语言能够实现的功能,就能够对复杂系统构造出清晰明了的结构。其实,Verilog HDL语言已被认为是事实上的ASIC行业标准。

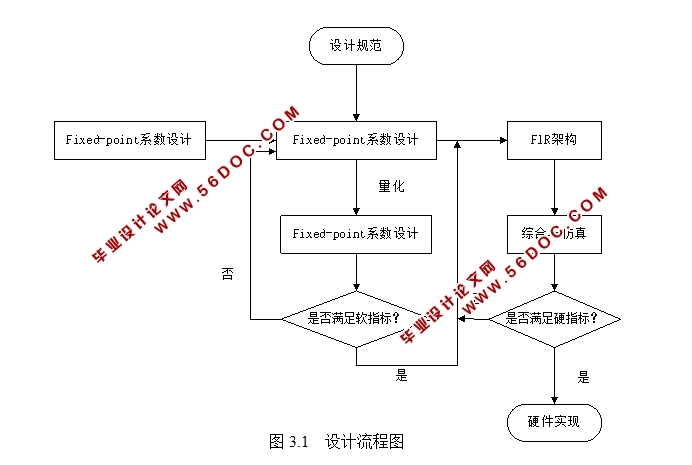

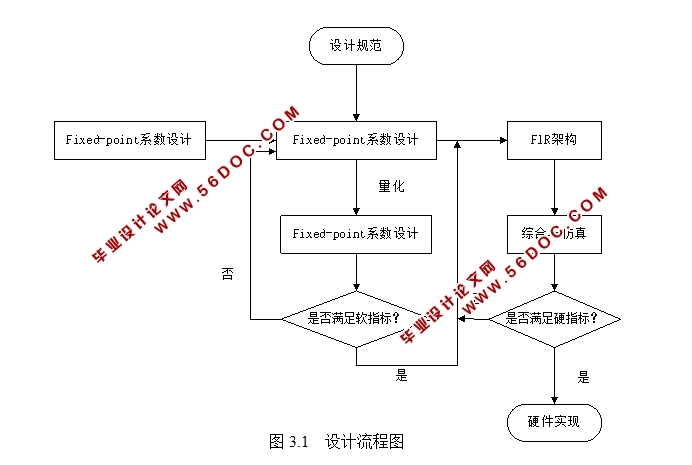

本文进行了串行FIR低通滤波器的FPGA设计。给出了串行FIR低通滤波器相关理论内容,FPGA相关理论,本课题研究实现方法、过程及结果。设计过程中用MATLAB软件获取系数,Verilog HDL语言编程。采用Quartus、NIOS软件和FPGA滤波器芯片设计仿真电路,示波器输出波形进行验证。实验结果相符,验证了该滤波器设计成功。

关键词:FIR低通滤波器;串行滤波; FPGA;Verilog HDL

Abstract

Life is related to signal, but it is mixed with many other useless noise and spread, causing serious damage to its quality. This filter is particularly crucial. For this reason, people in many signal using filter the useful part to stay, will filter out useless signal. Modern engineering priority in the use of digital systems, high efficiency, small size, fast speed, high performance characteristics. Therefore, gradually becomes the darling of the digital filter.

FIR (Finite Impulse Response) filter, as the name implies, limited number of sampling, convolution number to specify the precise linear phase, transfer process does not produce distortions in the production life of the popular project. Serial filter structure is simple, easy, low demand for filter order system of universal application.

Field-programmable gate arrays FPGA belongs to the ASIC, semi-custom circuits. It is very flexible to use, versatile, large scale, small size, field-programmable, you can complete a variety of complex functions of digital circuits. These benefits augmented the FPGA's reach in the production life, loved by the public.

Verilog HDL language in terms of digital circuit design is very popular. It simple and efficient, easy to use, yet very powerful, well all kinds of designers. Can realize the function using Verilog language, will be able to construct a clear structure of complex systems.In fact, Verilog HDL languages are considered to be de facto ASIC industry standards.

Conducted serial FPGA design of FIR low-pass filter. Gives the serial theory of FIR low-pass filter, FPGA-related theories, methods, processes and results of this research. MATLAB software used in the design process to obtain coefficients, Verilog HDL languages. Quartus II and NIOS II software and FPGA chip design and simulation of filter circuits, oscilloscope waveform for validation. Experimental results, the filter is verified successfully.

Key words: FIR low-pass filters; Series filtering; FPGA; Verilog HDL

目 录

摘 要 I

Abstract II

引 言 1

第一章 绪论 2

1.1 课题背景 2

1.2 研究的目的及意义 2

1.3 国内外研究现状 3

1.4 研究主要内容 3

第二章 串行FIR低通滤波器的FPGA设计原理 4

2.1 串行FIR低通滤波器基础理论 4

2.2 串行FIR低通滤波器的设计方法 5

2.2.1 窗函数法 5

2.2.2 频率采样法 8

2.2.3 FIR滤波器的优化 8

2.3 FPGA原理 9

2.3.1 可编程逻辑器件简介 9

2.3.2 FPGA的原理与结构 10

2.3.3 FPGA的基本设计流程 11

2.4 硬件描述语言Verilog HDL 11

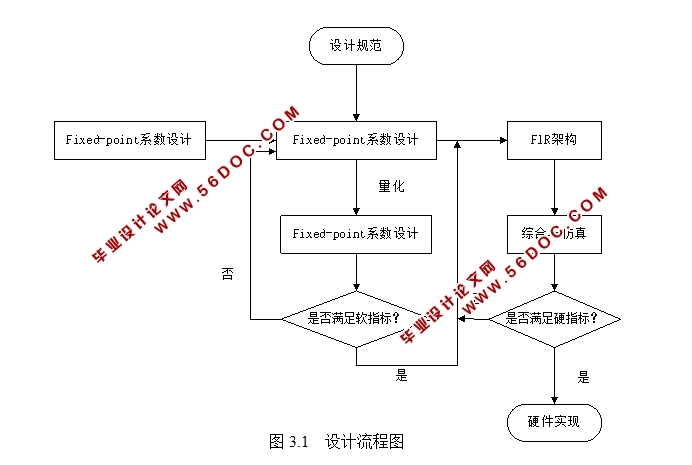

第三章 串行FIR低通滤波器的实现 14

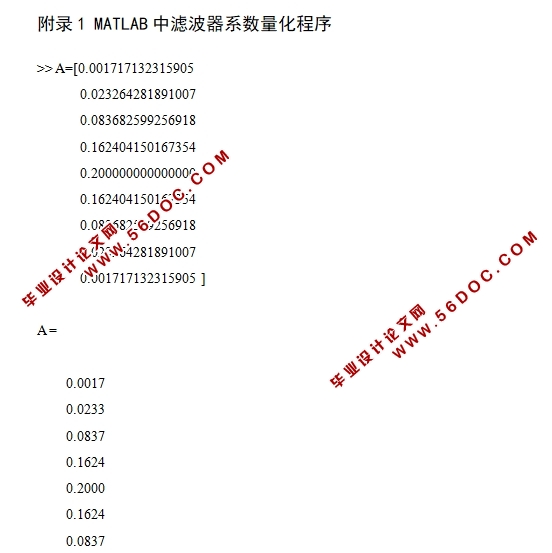

3.1 串行FIR低通滤波器的MATLAB设计 14

3.1.1 fir1函数 14

3.1.2 fir2函数 15

3.1.3 FDAtool工具 15

3.2 串行FIR低通滤波器的FPGA实现 20

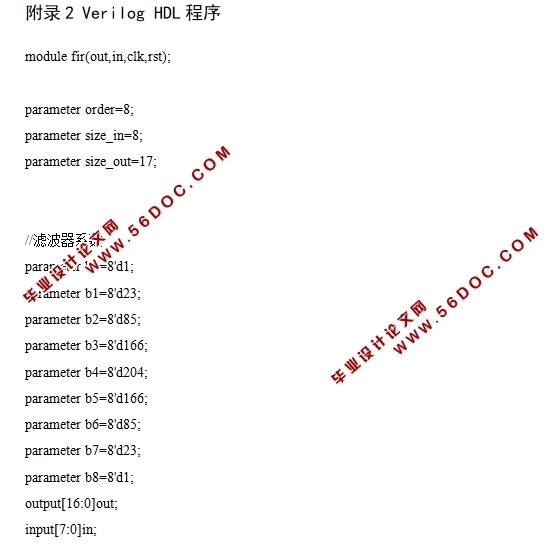

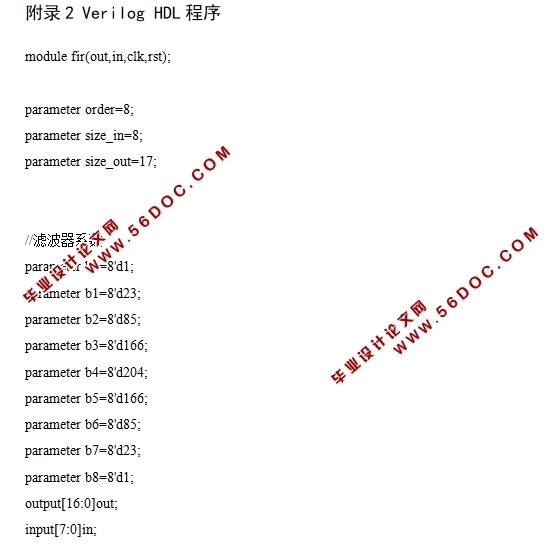

3.2.1 基于Verilog HDL的设计 20

3.2.2 基于FPGA的硬件设计 21

第四章 实验结果与分析 24

4.1 实验结果 24

4.2 结果分析 28

结 论 29

参考文献 30

谢 辞 31

附 录 32

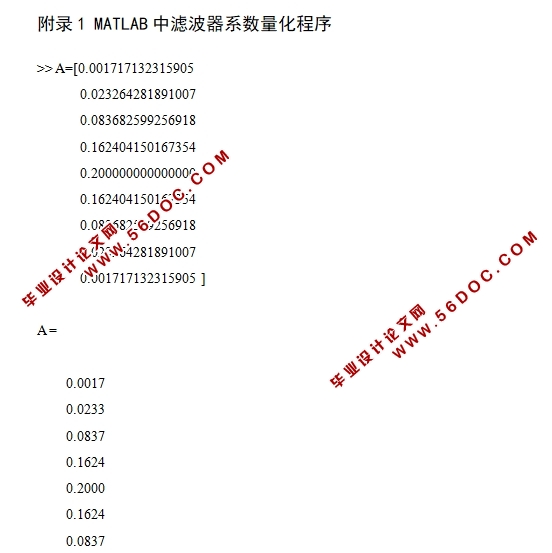

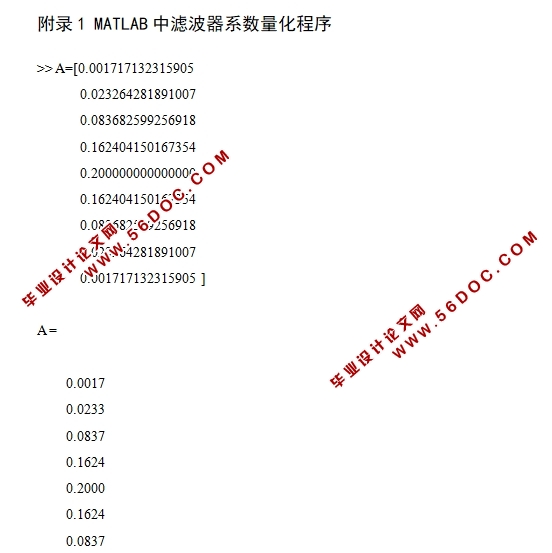

附录1 MATLAB中滤波器系数量化程序 32

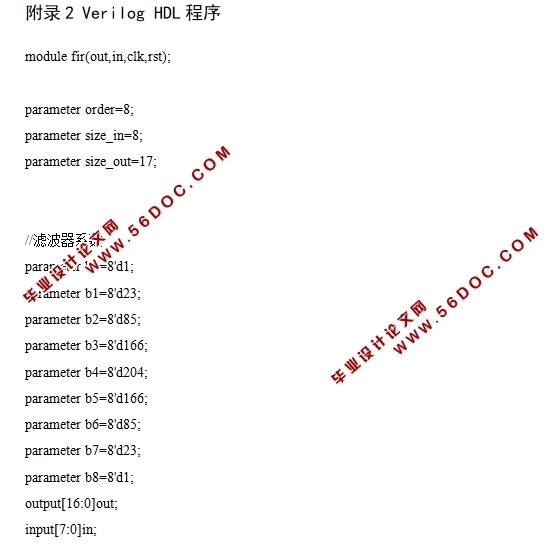

附录2 Verilog HDL程序 34

|